# **ADwin-X-A20** Manual

#### For any questions, please don't hesitate to contact us:

| Hotline: | - |

|----------|---|

| Fax:     | - |

| E-Mail:  | i |

| Internet | v |

+49 6251 96320 +49 6251 5 68 19 info@ADwin.de www.ADwin.de

Jager Computergesteuerte Messtechnik GmbH Rheinstraße 2-4 D-64653 Lorsch Germany

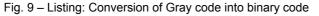

## Table of Contents

| Table of Contents III                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 Typografische KonventionenV                                                                                                                                                                                                                                                                                                                               |

| 1 Information about this Manual1                                                                                                                                                                                                                                                                                                                            |

| 2 System description                                                                                                                                                                                                                                                                                                                                        |

| 3 Operating Environment                                                                                                                                                                                                                                                                                                                                     |

| 4 Initialization of the Hardware                                                                                                                                                                                                                                                                                                                            |

| 5 Overview Inputs and Outputs                                                                                                                                                                                                                                                                                                                               |

| 6 X-A20 Basic       11         6.1 Multi-color LED.       11         6.2 Analog inputs, 18-bit       11         6.3 Analog outputs, 12-bit       14         6.4 Analog outputs, 12-bit       14         6.5 TTL digital channels DIO39:DIO32       15         6.6 Event Input       15         6.7 LS-Bus       16         6.8 Synchronous Actions       16 |

| 7 Option CO1                                                                                                                                                                                                                                                                                                                                                |

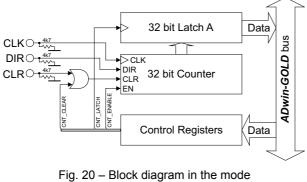

| 8 Option D         18           8.1 Diff. digital channels DIO47:DIO40         18           8.2 Diff. counters 4, 5         18           8.3 SSI interface         19                                                                                                                                                                                       |

| 9 Option DCT       21         9.1 TTL-digital channels DIO31:DIO00       21         9.2 Comparator inputs DIO59:DIO48       21         9.3 Edge control and Edge output       22         9.4 TTL Counters 2, 3       22         9.5 Comparator Counters 6, 7       23                                                                                       |

| 10 Option COM                                                                                                                                                                                                                                                                                                                                               |

### **Table of Contents**

## **ADwin**

| 11 Option Profibus                                                                                                                                                                                                                                                                                                                    | 27                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 12 Option Profinet-IRT                                                                                                                                                                                                                                                                                                                | 30                                                                   |

| 13 Option EtherCAT                                                                                                                                                                                                                                                                                                                    | 34                                                                   |

| 14 Option Boot                                                                                                                                                                                                                                                                                                                        | 37                                                                   |

| 15 Counter block                                                                                                                                                                                                                                                                                                                      | 40<br>41                                                             |

| 16 Software         16.1 General instructions         16.2 Analog Inputs and Outputs         16.3 Digital Inputs and Outputs         16.4 Counter         16.5 SSI interface         16.6 CAN interface         16.7 RSxxx Interface         16.8 Profibus interface         16.9 Profinet interface         16.10 EtherCAT interface | 46<br>53<br>77<br>. 110<br>. 127<br>. 135<br>. 146<br>. 152<br>. 156 |

| Annex         A.1 Technical Data.         A.2 Hardware revisions         A.3 RoHS Declaration of Conformity                                                                                                                                                                                                                           | . A-1<br>. A-6                                                       |

|                                                                                                                                                                                                                                                                                                                                       |                                                                      |

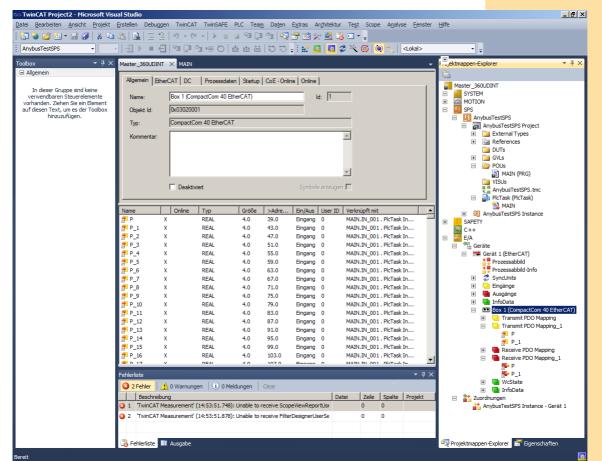

## 1 Typografische Konventionen

Das "Achtung"-Zeichen steht bei Informationen, die auf Folgeschäden durch Fehlbedienung an der Hard- oder Software, am Messaufbau oder an Personen hinweisen.

Einen "Hinweis" finden Sie bei

Dwin

- Informationen, die f

ür einen fehlerfreien Betrieb unbedingt beachtet werden m

üssen.

- Tipps und Ratschlägen für einen effizienten Betrieb.

Das Zeichen "Information" verweist auf weiterführende Informationen in dieser Dokumentation oder andere Quellen wie Handbücher, Datenblätter, Literatur etc.

Dateinamen und -verzeichnisse sind in spitzen Klammern und im Schrifttyp Courier New angeben.

Programmanweisungen und Benutzer-Eingaben sind durch den Schrifttyp Courier New gekennzeichnet.

Elemente eines Quelltextes wie Befehle, Variablen, Kommentar und sonstiger Text werden im Schrifttyp Courier New und farbig dargestellt.

In einem Datenwort (hier: 16 Bit) werden die Bits wie folgt nummeriert:

| Bit-Nr.       | 15              | 14              | 13              |   | 1                 | 0                 |

|---------------|-----------------|-----------------|-----------------|---|-------------------|-------------------|

| Wert des Bits | 2 <sup>15</sup> | 2 <sup>14</sup> | 2 <sup>13</sup> |   | 2 <sup>1</sup> =2 | 2 <sup>0</sup> =1 |

| Bezeichnung   | MSB             | -               | -               | - | -                 | LSB               |

Var 1

### 1 Information about this Manual

ADwin

This manual contains complex information about the operation of the *ADwin-X-A20* system. Additional information are available in

the manual "ADwin Installation", which describes all interface installations for the *ADwin* systems.

With this manual, you begin your installation!

- the description of the configuration program *ADconfig*, with which you initialize the communication from the corresponding interface to your *ADwin-X-A20* system.

- the manual ADbasic, which explains basic instructions for the compiler ADbasic and the functional layout of the ADwin system.

The online help of ADbasic contains the same information.

- the manuals for all current development environments containing the description of installation and instructions.

- installation and instruction manuals for drivers of all popular development environments

- the manual "ADwin HSM-24V" which describes a module for the LS bus.

Please note: This manual is still in progress, errors can be contained.

#### Please note:

For *ADwin* systems to function correctly, follow strictly the information provided in this documentation and in other mentioned manuals.

Programming, start-up and operation, as well as the modification of program parameters must be performed only by appropriately qualified personnel.

Qualified personnel are persons who, due to their education, experience and training as well as their knowledge of applicable technical standards, guidelines, accident prevention regulations and operating conditions, have been authorized by a quality assurance representative at the site to perform the necessary acivities, while recognizing and avoiding any possible dangers. (Definition of qualified personnel as per VDE 105 and ICE 364).

This product documentation and all documents referred to, have always to be available and to be strictly observed. For damages caused by disregarding the information in this documentation or in all other additional documentations, no liability is assumed by the company *Jäger Computergesteuerte Messtechnik GmbH*, Lorsch, Germany.

This documentation, including all pictures is protected by copyright. Reproduction, translation as well as electronical and photographical archiving and modification require a written permission by the company *Jäger Computergesteuerte Messtechnik GmbH*, Lorsch, Germany.

OEM products are mentioned without referring to possible patent rights, the existence of which may not be excluded.

Hotline address: see inner side of cover page.

Availability of the documents

**Qualified personnel**

Subject to change.

|                            | 2 System description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | 2.1 ADwin system concept                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                            | <b>ADwin</b> systems guarantee fast and accurate operation of measurement data acquisition and automation tasks under real-time conditions. This offers an ideal basis for applications such as:                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                            | <ul> <li>very fast digital closed-loop control systems</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                            | <ul> <li>very fast open-loop control systems</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                            | <ul> <li>data acquisition with very fast online analysis of the measurement data</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                            | <ul> <li>monitoring of complex trigger conditions and many more</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                            | <i>ADwin</i> systems are optimized for processes, which need <b>very short process cycle times</b> of one millisecond down to some microseconds.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

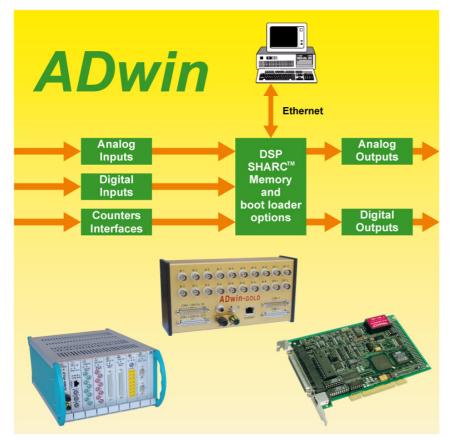

| System features            | The <b>ADwin</b> system is equipped with analog and digital inputs and outputs, a fast pro-<br>cessor (32-bit or 64-bit floating-point signal processor) and local memory. The proces-<br>sor is responsible for the whole real-time processing in the system. The applications run<br><b>independent</b> of the PC and its workload.                                                                                                                                                                                                                                                                                                              |

| Processor                  | The processor of the ADwin system processes each measurement value at once.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                            | In one cycle, you can acquire the status of the inputs, process the status with the help<br>of any mathematical functions, and react to the results, even at very fast process cycle<br>times of some microseconds. This results in a perfect and logical work sharing: The PC<br>executes a program for visualizing of data, for input and operation of the processes,<br>togeher with access to networks and data bases, while the processor of the <i>ADwin</i> sys-<br>tem executes all tasks, which require real-time processing concurrently.                                                                                                |

| Real-time operating system | The operating system for the DSP of the <i>ADwin</i> system has been optimized to achieve<br>the fastest response times possible. It manages parallel processes in a <b>multitasking</b><br>environment. Low priority processes are managed by time slicing. Specified high prior-<br>ity processes interrupt all low priority processes and are immediately and completely<br>executed (preemptive multitasking). High priority processes are executed as time-con-<br>trolled or event-controlled processes (external trigger).                                                                                                                  |

| Timing                     | The built-in <b>timer</b> is responsible for the precise scheduling of high priority processes. It has a resolution of 25 nanoseconds (3,3ns since processor T11). The <i>ADwin</i> systems are characterized by an extremely short response time of only 300 nanoseconds during the change from a low to a high priority process. A continuously running communication process enables a continuous data exchange between the <i>ADwin</i> system and the PC even while applications are active. The communication has no influence on the real-time capability of the <i>ADwin</i> system, even so, it is possible to exchange data at any time. |

| ADbasic                    | The real-time development tool <i>ADbasic</i> gives the opportunity to create time-critical programs for <i>ADwin</i> systems very easily and quickly. <i>ADbasic</i> is an <b>integrated development environment</b> under Windows with possibilities of online debugging. The familiar, easy-to-learn BASIC instruction syntax has been extended by many more functions, in order to allow direct access to inputs and outputs as well as by functions for process control and communication with the PC.                                                                                                                                        |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### Communication between ADwin system and PC

The *ADwin* system is connected to the PC via an **USB or Ethernet** interface. After power-up the *ADwin* system is booted from the PC via this interface. Afterwards the *ADwin* operating system is waiting for instructions from the PC, which it will process.

There are two kinds of instructions: On the one hand instructions, which transfer data from the PC to the *ADwin* system, for instance "load process", "start process" or "set parameter", on the other hand instructions, which wait for a response from the *ADwin* system, for instance "read variables" or "read data sets". Both kinds of instructions are processed immediately by the *ADwin* system, which means immediate and complete responses. The *ADwin* system never sends data to the PC without request! The data transfer to the PC is always a response to an instruction coming from the PC. Thus, embedding the *ADwin* system into various programming languages and standard software packages for measurements is held simple, because they have only to be able to call functions and process the return value.

Under Windows 95/98/NT/ME/2000/XP/Vista, you can use a **DLL** and an **ActiveX** interface. On this basis the following drivers for **development environments** are available: .NET, Visual Basic, Visual-C, C/C++, Delphi, VBA (Excel, Access, Word), TestPoint, LabVIEW / LabWINDOWS, Agilent VEE (HP-VEE), InTouch, DIAdem, DASYLab, SciLab, MATLAB.

Versions for Linux, Mac OS and Java are available, too.

The simple, instruction-oriented communication with the *ADwin* system enables several Windows programs to access the same *ADwin* system in coordination at the same time. This is of course a great advantage when programs are being developed and installed.

Fig. 1 – Concept of the *ADwin* systems

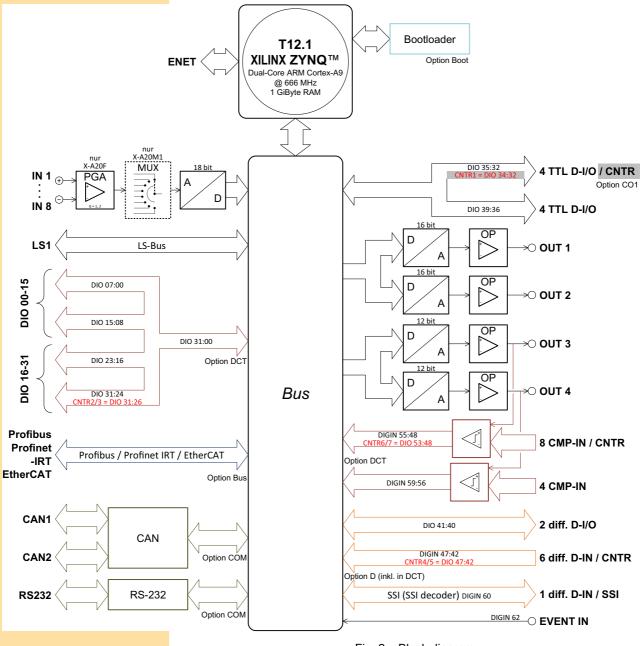

#### 2.2 ADwin-X-A20

ADwin-X-A20 is euqipped with the digital **signal processor** XILINX ZYNQ<sup>™</sup> with Dual-Core ARM Cortex-A9 (666MHz), which processes 64 bit float and 32 bit integer. It is responsible for the complete measurement data acquisition, online processing, and signal output, and makes it possible to instantaneously process sample rates in the range of 200 Kilohertz to 1 Megahertz. **Prozessor und Speicher**

Software interfaces

The **memory 1 GiB** is large enough for all tasks and even bulk data. An integrated cache memory allows very short access time and holds the complete *ADwin* operating system, *ADbasic* processes and all variables.

In order to get maximum access times, all inputs and outputs are memory-mapped in the external memory section of the DSP.

The number and function of inputs and outputs differ according to the selected variant of X-A20. The following text describes all available functions.

**Analog inputs**

The system has 8 analog inputs (differential) on a DSub connectors. The input signals are converted by a 18-bit analog-to-digital converter (ADC), see Fig. 2 "Block diagram". According to the *ADwin-X* version, the sampling sequence converts the digital value of one channel (X-A20-M1) or of up to 8 channels synchronously (X-A20-F).

**Analog outputs**

Fig. 2 – Block diagram

*ADwin-X-A20* is equipped with **2** analog outputs of **16-bit resolution** with an output voltage range of -10V ... +10V. You can synchronize the voltage output of all DACs via software. The output signal is smoothed by a low-pass filter with a cut-off frequency of  $f_g = 700$  kHz.

There are also **2** analog outputs with **12-bit resolution**, conversion rate 1ms. The output signals are internally used for comparator inputs and counters.

### System description

| 32 digital inputs or outputs are available on D-Sub connectors. They can be pro-<br>grammed in groups of 8 as inputs or outputs. The inputs or outputs are TTL-compatible.                                                                                                                                                                                                                                                        | Digital inputs and outputs |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| D-Sub connectors provide a range of 8 to 61 <b>digital inputs and outputs</b> , according to the <i>ADwin-X</i> version. Generally, the digital channels are TTL-compatible, but there are also 8 differential channels and 8 comparator inputs. Most channels can be programmed in groups as inputs or outputs, but some are already fixed. Partly, digital channels have double allocation and are also used as counter inputs. |                            |

| Using a FIFO, an edge control of digital inputs is available. With digital outputs, FIFOs allow to output edges at specified points in time.                                                                                                                                                                                                                                                                                      |                            |

| There are overall <b>7 counter blocks</b> with 32-bit; a counter block provides one up/down counter and one PWM counter. Counter blocks are equal in function but can process different inputs signals: TTL-like signals, differential signal, comparator signals.                                                                                                                                                                | Counters                   |

| <i>ADwin-X-A20</i> has a trigger input (EVENT, see also page 15). Processes can be trig-<br>gered by a signal and are completely processed afterwards. (see <i>ADbasic</i> manual, chapter "Processes in the <i>ADbasic</i> System").                                                                                                                                                                                             | Trigger input (EVENT)      |

| Using the LS bus interface (see page 16), up to 15 LS bus modules can be addressed.<br>The LS bus module HSM-24V provides 32 digital channels for 24 Volt signals.                                                                                                                                                                                                                                                                | 24 Volt signals            |

| There are interfaces for CAN (High Speed), RS232, SSI, Profibus, Profinet-IRT, and EtherCAT. More interfaces are available on request.                                                                                                                                                                                                                                                                                            | Schnittstellen             |

| The Bootloader starts a previously programmed application automatically after power-<br>up. After installation of this application, an operation without computer is possible.                                                                                                                                                                                                                                                    | Bootloader                 |

| The standard delivery items for ADwin-X-A20:                                                                                                                                                                                                                                                                                                                                                                                      | Standard delivery          |

| <ul> <li>Hardware ADwin-X-A20 (Design and Functions as ordered).</li> </ul>                                                                                                                                                                                                                                                                                                                                                       |                            |

| <ul> <li>Cross-over Ethernet cable, length 1.8 meters.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                 |                            |

| <ul> <li>Three-pole power supply cable with one power supply plug, length 1.0 meters.</li> </ul>                                                                                                                                                                                                                                                                                                                                  |                            |

| The open cable end is used for connection to the external power supply (self-as-<br>sembly); see appendix for power supply characteristics.                                                                                                                                                                                                                                                                                       |                            |

| <ul> <li>ADwin software package.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                       |                            |

| <ul> <li>Manual "Driver Installation".</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                 |                            |

| - This manual.                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |

| 2.2.1 Design                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |

| ADwin-X-A20 is available in the following designs:                                                                                                                                                                                                                                                                                                                                                                                |                            |

| <ul> <li>Standard: Metal enclosure as desktop unit.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                    |                            |

| <ul> <li>A20-R: Metal enclosure for installation in 19" racks. All +Bus options (PROFI-<br/>BUS, PROFINET, ECAT, see below) are not available.</li> </ul>                                                                                                                                                                                                                                                                         |                            |

#### 2.2.2 Functions

*ADwin-X-A20* as basic version is available as *X-A20-M1* or *X-A20-F*. The basic version can be combined with any of several opptions.

| Option      | IS             | Functions                                                                                              | Page    |

|-------------|----------------|--------------------------------------------------------------------------------------------------------|---------|

| X-A20 Basic |                | 8 analog inputs, 18-bit<br>2 analog outputs, 16-bit<br>2 analog outputs, 12-bit                        | page 11 |

|             |                | 8 TTL digital channels<br>1 Event input                                                                | page 11 |

|             |                | 1 LS bus interface                                                                                     | page 16 |

|             | M1             | Analog inputs with multiplexer: 1 measurement value per conversion, 200kHz.                            |         |

|             | F              | Analog input, fast: up to 8 measurement values converted synchronously, 200kHz800kHz; gain selectable. |         |

| +CO1        |                | 1 TTL counter block: 32-bit up/down counter and PWM counter                                            | page 17 |

| +DCT        |                | 32 TTL digital channels                                                                                | page 21 |

| (inklus     | ive D)W        | 12 comparator inputs                                                                                   |         |

|             |                | 2 TTL counter blocks: 32-bit up/down counter and PWM counter                                           |         |

|             |                | 2 comparator counter blocks: 32-bit up/down counter and PWM counter                                    |         |

|             |                | Input FIFO and output FIFO for digital channels                                                        |         |

|             | +D             | 6 diff. digital inputs + 2 diff. digital channels                                                      | page 18 |

|             |                | 2 differential counter blocks: 32-bit up/down counter and PWM counter                                  |         |

|             |                | 1 SSI interface                                                                                        |         |

| +COM        |                | 2 CAN interfaces (high speed)                                                                          | page 24 |

| 1 RS        |                | 1 RS232 interface                                                                                      |         |

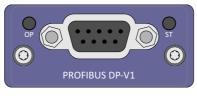

| +Bus        | +PROFI-<br>BUS | 1 Profibus interface (Slave)                                                                           | page 27 |

|             | +PROFI-<br>NET | 1 Profinet-IRT interface (Slave)                                                                       | page 30 |

|             | +ECAT          | 1 EtherCAT-Schnittstelle (Slave)                                                                       | page 34 |

| +Boot       |                | Flash EPROM bootloader for independent pro-<br>cessing without PC                                      | page 37 |

Option DCT is expansion of option D, so these two options cannot be combined. Options PROFIBUS, PROFINET, and ECAT cannot be combined.

#### 2.2.3 Accessories

For ADwin-X-A20, the supplementary accessories are availabe:

- ADbasic, real-time development tool for all ADwin systems.

- A20-Mount: A20 mount: Housing for DIN rail mounting in a switch cabinet with insulated clips.

- A20-Pow: external power supply.

- A20-Pow-Mount: external power supply for DIN rails.

- HSM-24V: DIN rail module for LS bus interface, 32 digital I/Os, 24V level, configurable in groups of 8, screw terminals.

### **3** Operating Environment

With the necessary accessories, the system can be operated in 19-inch-enclosures or as a mobile system (e.g. in cars).

The ADwin-X-A20 device must be earth-protected, in order to

- build a ground reference point for the electronic

- conduct interferences to earth.

Connect the GND plug, which is internally connected with the ground reference point and the enclosure, via a short low-impedance solid-type cable to the central earth connection point of your device.

The data lines at the version with Ethernet interface are optically isolated, but the ground potentials are connected, because the shielding of the Ethernet connector (RJ-45) is connected to GND.

Transient currents, which are conducted via the aluminum enclosure or the shielding, have an influence on the measurement signal.

Please, make sure that the shielding is not reduced, for instance by taking measures for bleeding off interferences, such as connecting the shielding to the enclosure just before entering it. The more frequently you earth the shielding on its way to the machine the better the shielding will be.

Use cables with shielding on both ends for signal lines. Here too, you should reduce the bleeding off of interferences via the enclosure by using screen clips.

The *ADwin-X-A20* is externally operated with a protection low voltage of 10V to 35V; internally it is operated with a voltage of +5V and  $\pm 15V$  against GND. It is not life-threatening. For operation with an external power supply, the instructions of the manufacturer applies.

The *ADwin-X-A20* is designed for operation in dry rooms with a room temperature of  $+5^{\circ}$ C ...  $+50^{\circ}$ C and a relative humidity of 0 ... 80% (no condensation, see Annex).

The temperature of the chassis (surface) must not exceed +60°C, even under extreme operating conditions – e.g. in an enclosure or if the system is exposed to the sun for a longer period of time. You risk damages at the device or not-defined data (values) are output, which can cause damages at your measurement device under unfavorable circumstances.

|                              | 4 Initialization of the Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (P)                          | If you start initializing do not connect any cables to the <i>ADwin-X-A20</i> before you have executed the following steps:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                              | 1. Software installation / installation in PC or 19" enlosure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                              | Follow the manual "ADwin Driver Installation".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                              | 2. Set the operating environment, see chapter 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                              | 3. Read chapter 5 "Overview Inputs and Outputs" in this manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              | 4. Begin now with the connection of the inputs and outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                              | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Providing the power supply   | Please pay attention that reliable power source is supplied.<br>This concerns the computer (standard delivery). Otherwise also the external power<br>supply, if operated in a car, the battery voltage.<br>If using current-limiting power supplies, please pay attention to the fact, that after<br>power-up the current demand can be a multiple of the idle current. More detailed infor-<br>mation can be found in the Technical Data (Annex).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                              | In case of a power failure, all data, which have not been saved are lost. Not-defined data (values) can under unfavorable circumstances cause damages to other equipment.<br>Avoid direct contact to uninsulated parts to be secure of electrostatic charging.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                              | Checking the Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Booting                      | Start ADbasic and boot the ADwin system by clicking on the boot button B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Programs with <i>ADbasic</i> | ADbasic - [ADbasic1]         File       Edit       Yiew       Build       Options       Debug       Tools       Window       Help         Image: Ima |

|                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

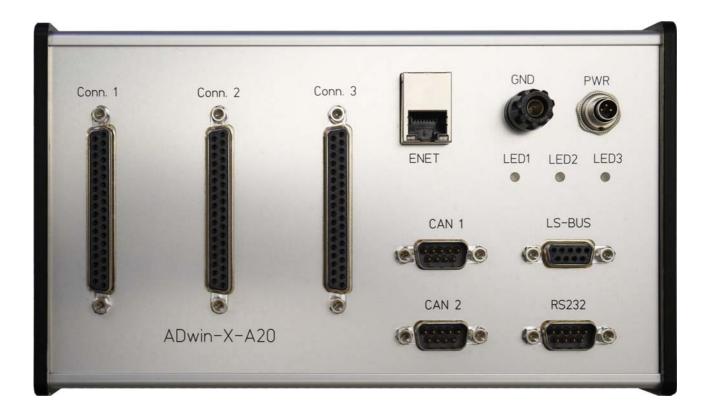

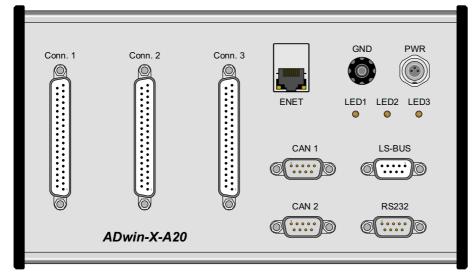

## 5 Overview Inputs and Outputs

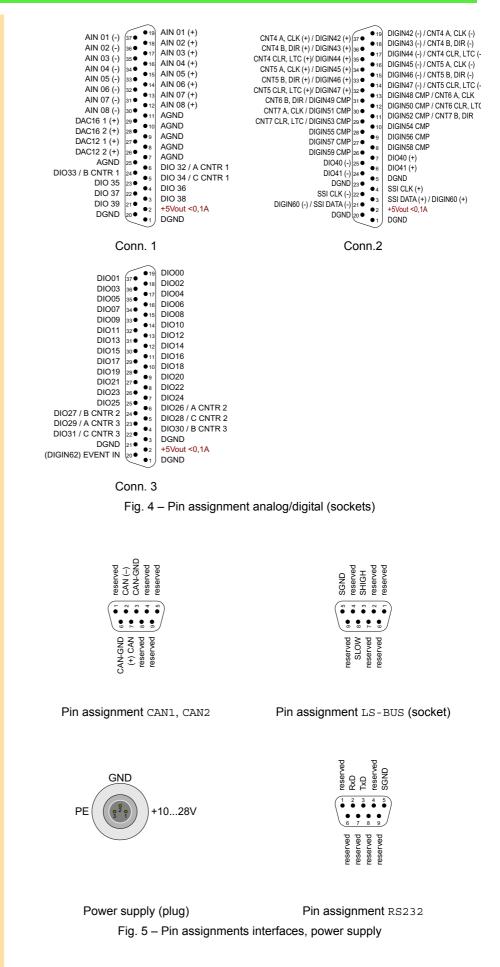

*ADwin-X-A20* provides the following inputs and outputs (Pin assignment see next page). According to the built-in optionsm, only some of the pins may be used.

- Ethernet connector

- Power supply connector

- GND connector

- 3 D-Sub sockets, 37-pole: Conn. 1, Conn. 2, Conn. 3

- analog inputs, analog outputs

- · digital inputs and outputs: TTL, differential, comparator

- inputs for counters: TTL, differential, comparator

- SSI interface

- digital trigger input (Event)

- power output +5V

Some pins have double assignments.

- 2 D-Sub plugs 9-pole, CAN1, CAN2

- 1 D-Sub plug 9-pole, RS232

- 1 D-Sub socket 9-pole, LS-BUS

Fig. 3 – Connectors of ADwin-X-A20

All inputs and outputs may only be operated according to the specifications given (see Annex A.1 Technical Data). In case of doubt, ask the manufacturer of the device, to which you want to connect *ADwin-X-A20*.

Open-ended inputs can cause errors - above all in an environment where interferences may occur. For your safety, set the inputs, which you do not use to a specified level (for instance GND) and also connect them as close to the connector as possible. Don't connect open ended cables to the inputs; open ended cables may cause spikes at the inputs.

The event input is an exception, it has an internal pull-up resistor (4.7 k $\Omega$ ).

### 6 X-A20 Basic

The basic version of X-A20 comprises:

- 3 Multi-color LED

- 8 Analog inputs, 18-bit

- X-A20-M1: Multiplexer

- X-A20-F: Synchronous conversion

- 2 Analog outputs, 12-bit

- 2 Analog outputs, 16-bit

- 8 TTL digital channels DIO39:DIO32

- 1 Event Input

- 1 LS-Bus

- Synchronous Actions

#### 6.1 Multi-color LED

X-A20 provides 3 multi-color LEDs, which you can switch on and off.

After power-up, LED 1 serves as status LED and glows red; as soon as boot processing has finished, Process 15 is running and makes LED 1 blink green.

Instructions to program LEDs are described starting from page 47 and in the online help. The instructions are defined in the include file ADwin-X.inc.

| Function                        | Instructions |

|---------------------------------|--------------|

| Check LED status                | Check_LED    |

| Switch LED on or off, set color | Set_LED      |

#### 6.2 Analog inputs, 18-bit

*X-A20* provides 8 differential analog measuring inputs, which run via a 18-bit analog digital converter (ADC). There are two variants:

X-A20-M1: Multiplexer

The 8 analog measuring inputs are allocated to a multiplexer and from there connected to a 18-bit-ADC. The conversion time is  $5\mu s$  (including multiplexer settling time). The gain factor is set to 1.

- X-A20-F: Synchronous conversion

Up to 8 analog measuring inputs are converted synchronously. The gain (PGA) is programmable to 1 or 2. The conversion time (for all channels together) depends on the number of converted channels:

- 1 channel: max. 800kHz = 1.25µs.

- 2 channels: max. 550kHz = 1.82µs.

- 3 channels: max. 425kHz = 2.35µs.

- 4 channels: max. 350kHz = 2.86µs.

- 5 channels: max.  $300 \text{ kHz} = 3.3 \mu \text{s}$ .

- 6 channels: max. 250 kHz = 4.0 µs.

- 7 channels: max. 225kHz = 4.44µs.

- 8 channels: max. 200 kHz = 5  $\mu$ s.

If you select different channels with a conversion instruction (ADC... / Start\_Conv) than with the previous conversion instruction, the conversion time is extended: With the change, the conversion is processed twice, once with the previously selected channels and once with the newly selected channels.

The input voltage range is  $\pm 10V$  (with gain factor 1).

The analog inputs are differential.For each of the measurement inputs there is a positive and a negative input, between them the voltage difference is measured (but not free of potential). Both, the positive and negative input have to be connected, see Fig. 4 – Pin assignment analog/digital (sockets).

Please note, that the inputs do need a mass connection between the system's GNDplug and the signal source. This is in addition to the connections to the positive and negative input.

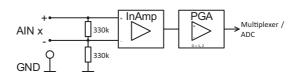

Fig. 6 - Input circuitry of an analog input

Signals are converted fast and accurately (76µV) with the 18-bit analog-to-digital-converter (ADC). Measurement values can be returned with 16 bit or 24 bit resolution.

Please note the Calculation Basics for evaluation of measurement values.

With X-A20-F there are two alternative options to convert measurement values. With X-A20-M1 both methods are available, but only with a single channel:

- Single conversion: The conversion of one or several channels is started at a defined time and the measurement value(s) is returned in the appropriate time. Each conversion has to be started on its own.

- Continuous conversion: A sequential control continuously converts measurment values on one or several selected channels. You can read the current value without waiting, but the exact time of conversion is unknown. Thus, the processor can be discharged a lot and only has to read completely converted values from the sequential control's buffer.

X-A20 must be earth-protected, in order do measurements free of interference. Connect the GND plug via a short low-impedance solid-type cable to the central earth connection point of your device.

The enclosure is connected to GND via the GND wire of the power supply cable as well as via the shiedling of the Ethernet cable.

The power supply via the power adapter at the PC links the ground potential of the ADwin-X-A20 with the PC. A voltage difference between ground potentials interferes with operation and can change measurements or cause considerable damage. Avoid disturbances by using an external power supply.

The standard instruction ADC () processes a complete measurement with the ADC on one channel (see page 58) and returns a 16-bit value.

You get measurement values with 18-bit resolution with the instruction ADC24 (see page 59); the value is returned as a 24-bit value (see page 16).

Both instructions use the 18-bit-ADC, only the return values have different formats.

Please pay attention to a low output resistance of the signal source (of the input signals), because it may have influence on the measuring accuracy. If this is not possible:

Depending on the output resistance a linear error is caused (about 1 digit per 10Ω).

You can compensate this by multiplying the measurement value with a corresponding factor and get a sort of re-calibration.

Instructions to program analog inputs (both X-A20-M1 and X-A20-F) are described starting from page 58 and in the online help. The instructions are defined in the include file ADwin-X.inc.

| Function                                                                | Instructions                                     | -M1 | -F |

|-------------------------------------------------------------------------|--------------------------------------------------|-----|----|

| Do a complete conversion                                                | ADC, ADC24                                       | х   | х  |

| Do conversions on several channels                                      | ADC2, ADC4, ADC8<br>ADC_2_24, ADC4_24<br>ADC8_24 | -   | х  |

| Do a measurement in steps, start contin-<br>uous measurement            | Start_Conv, Wait_EOC<br>Read_ADC, Read_ADC24     | х   | х  |

| Set gain (and start conversion)                                         | Start_Conv_PGA                                   | -   | х  |

| Read several measurement values at the same time (measurement in steps) | Read_ADC_Packed<br>Read_ADC8<br>Read_ADC8_24     | -   | х  |

| Start several functions synchronously.                                  | Sync_All                                         | Х   | Х  |

Earth protection

#### Standard instruction

Programming

#### 6.2.1 Calculation Basics

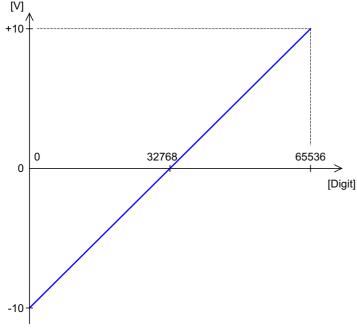

The voltage range of the *ADwin-X-A20* at the analog inputs and outputs is between -10V to +10V or bipolar 10V.

The 65536 ( $2^{16}$ ) digits are allocated to the corresponding voltage ranges of the ADCs and DACs so that  $^1$

- 0 (zero) digits correspond to the maximum negative voltage and

- 65535 digits correspond to the maximum positive voltage

The value for 65536 digits, exactly +10 Volt, is just outside the measurement range, so that you will get a maximum voltage value of +9.999695V for a 16-bit conversion.

Fig. 7 – Zero offset in the standard setting of bipolar 10 Volts

In the bipolar setting, you will get a zero offset, also called offset  $\mathsf{U}_{\mathsf{OFF}}$  in the following text.

For the voltage range of -10V ... +10V applies:  $U_{OFF} = -10V$

*X-A20-F* has a programmable gain (PGA), which can amplify the input voltage by the factors 1 ( $\pm$ 10V) or 2 ( $\pm$ 5V). The gain factor also changes the measurement range. Please note that with a gain factor k<sub>V</sub>=2, interference signals are amplified respectively.